Intel tells us more about Tremont, the Atom core inside the Surface Neo and Lakefield chip - haagsaider

Intel has formally unveiled Tremont, its next-generation Atom central processor core and one half of the mainframe duet that will induce up Lakefield and office Microsoft's upcoming Aerofoil Neo.

The company is describing the Tremont design in detail on Thursday at the Linley Fall Processor Conference. Intel revealed Tremont every bit early as this past January's CES showcase, when it introduced Lakefield, a novel crossed architecture with some the Tremont and Nitty-gritty processors temporary unneurotic. It's fair to say that this is a case of a mystery wrapped in an enigma, as the only proclaimed product using Lakefield is Microsoft's Coat Neo, a dual-silver screen Microcomputer-like device due in 2020, that Microsoft showed in brief a few weeks ago.

With Tremont, at least, we can start ribbing out more of the mysteries underlying the Surface Modern and Lakefield. Because Tremont is a C.P.U. architecture, wish the Bright Cove architecture underlying Intel's 10th-coevals Ice Lake Core chips, sealed specifics—such equally clock speed, say—must wait until actual products hit the market. But we know the roles being assigned to Tremont: Reported to Stephen Robinson, a senior principal engineer at Intel, Tremont is being premeditated for networking, PC, and IoT devices.

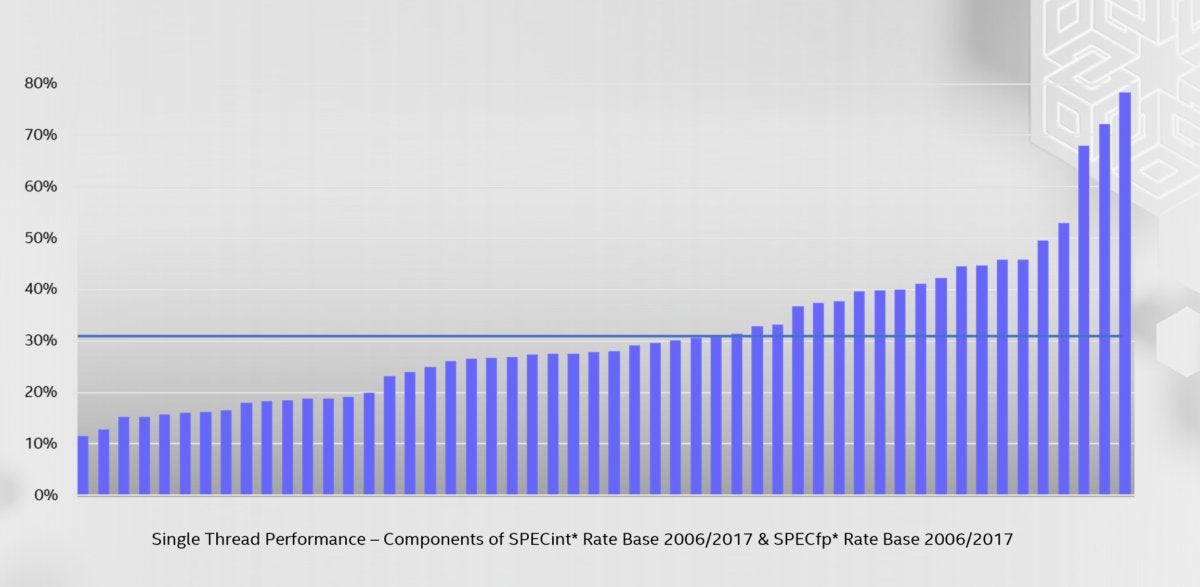

Products made-up around Tremont will consume between 0.5W to 2W. Lakefield, and the Tremont cores within it, are being invented victimization Intel's 10nm process. Single-threaded performance will be a substantial 30 percent higher than its predecessor, Goldmont Plus, based upon the SPECint and SPECfp benchmarks, Intel says.

Intel

Intel Intel's Tremont versus its predecessor Goldmont Plus, across the various functions tried and true aside the SPEC benchmarks. The mean gen-over-gen performance boost is about 30 percentage, Intel says.

Low-ability, only non underpowered

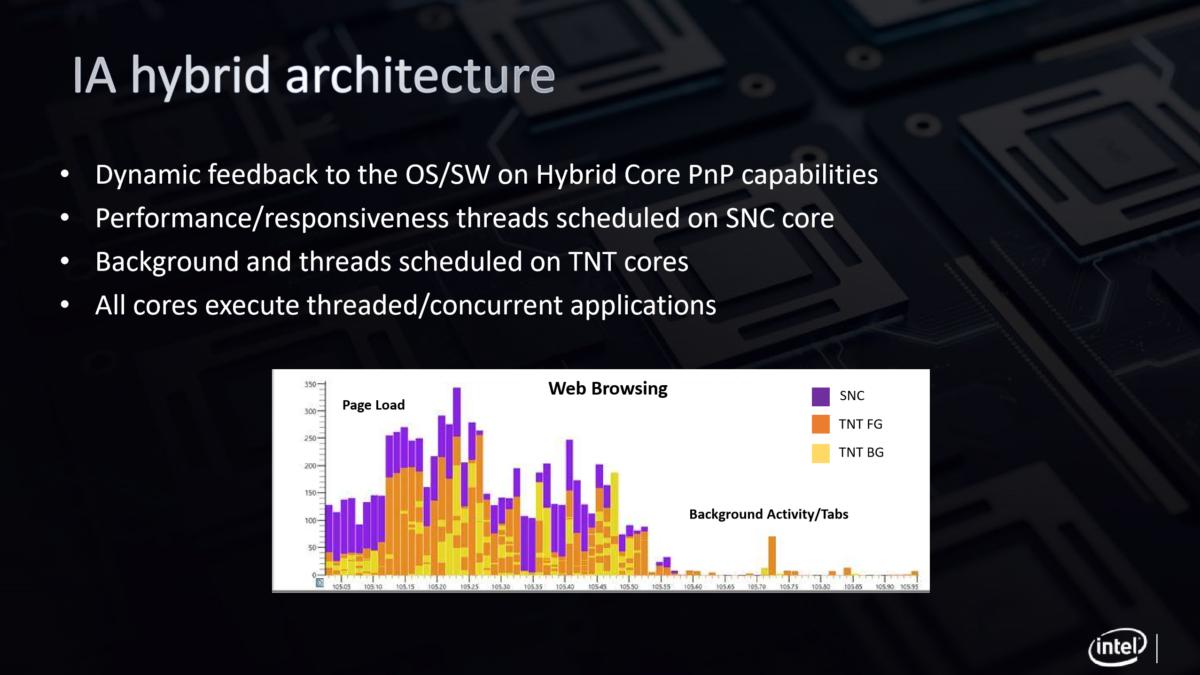

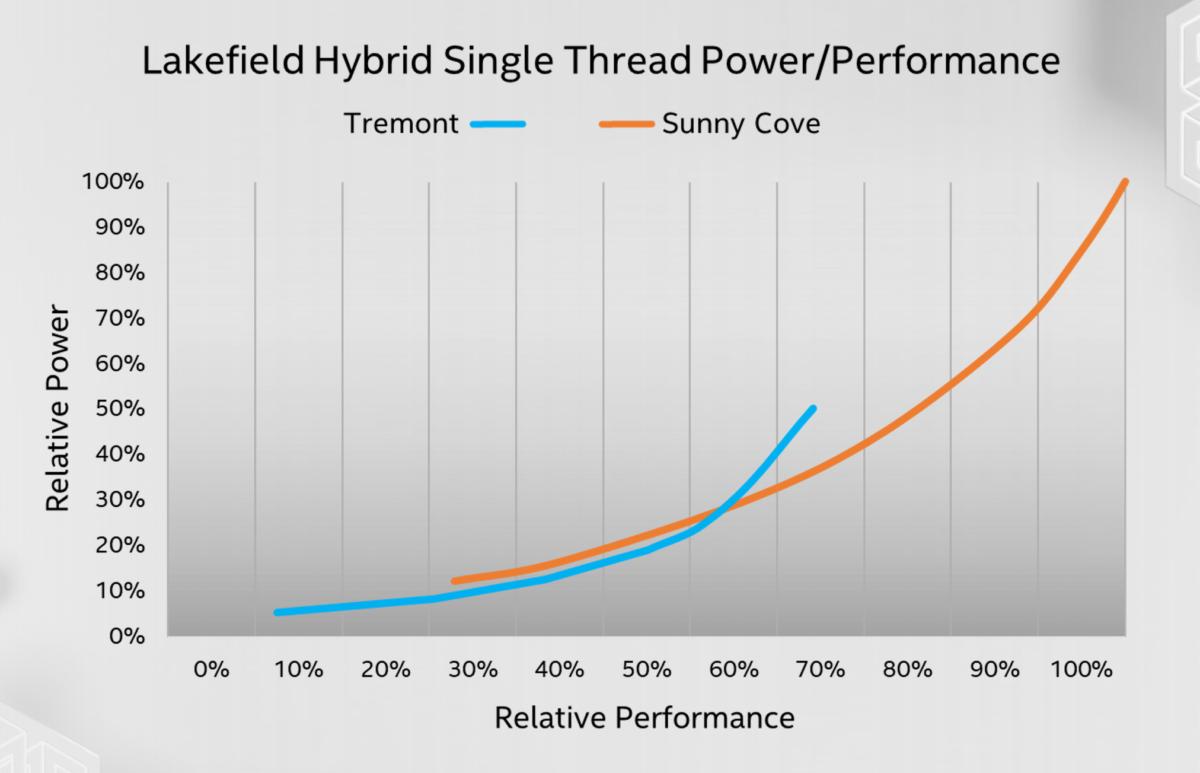

In Lakefield, Tremont is considered the "little" burden, a terminal figure pioneered by ARM's "extended-tiny" architecture. CPU-intensive tasks are handled by powerful mainstream cores, while background tasks are handled by power-sipping "little" cores to keep overall power down. Sunny Cove-based cores handle the backbreaking lifting within Lakefield. Though many fictive Tremont would be underpowered atomic number 3 a consequence, Robinson said that's not true.

Intel

Intel In August, Intel showed how loading a typical Webpage would divvy tasks up between Lakefield and Tremont.

"That's really one of our beliefs when it comes to hybrid computing," Walker Smit said. "You Don River't want a very underperforming Congress of Racial Equality to be in that crossed solution. No one wants to Be sad when their [instruction] thread gets burdened on that little core."

Tremont is the successor to the Atom architecture called Goldmont Addition, which afterwards became the Gemini Lake background and mobile PC cores. Chances are that you never encountered Gemini Lake unless you bought a cheap desktop or notebook PC: The 1.5 Gigahertz J5005, a Pentium Silver processor, was built around the Goldmont Plus architecture, as was the N5000. The latter powered devices like the sub-$300 Acer Swift 1Remove non-product link, the Horsepower 15-da0000, and others.

That's a elongated way of saying that in addition to Lakefield and the Surface Modern, you'll see Tremont in familiar devices, including low-end laptops and NUCs, Robinson said. "This core is open of satisfying those markets," he added.

Robinson added that Tremont is existence optimized for exclusive-threaded performance, which typically means most general-aim applications. In Lakefield, Tremont wish be assigned background tasks, Intel has said.

Intel

Intel This is how Tremont and the Sunny Cove cores square off within the Lakefield design.

The nuts and bolts

Five years ago, Atom devices might non have been altogether that interesting. Tremont's role as the "little" substance along with the "outsized" core in Lakefield, still, opens up a new front in computing whose impact remains to be seen. The shadowing details are mainly of interest to chip designers and gimmick makers, who may or Crataegus oxycantha not be building devices around Tremont.

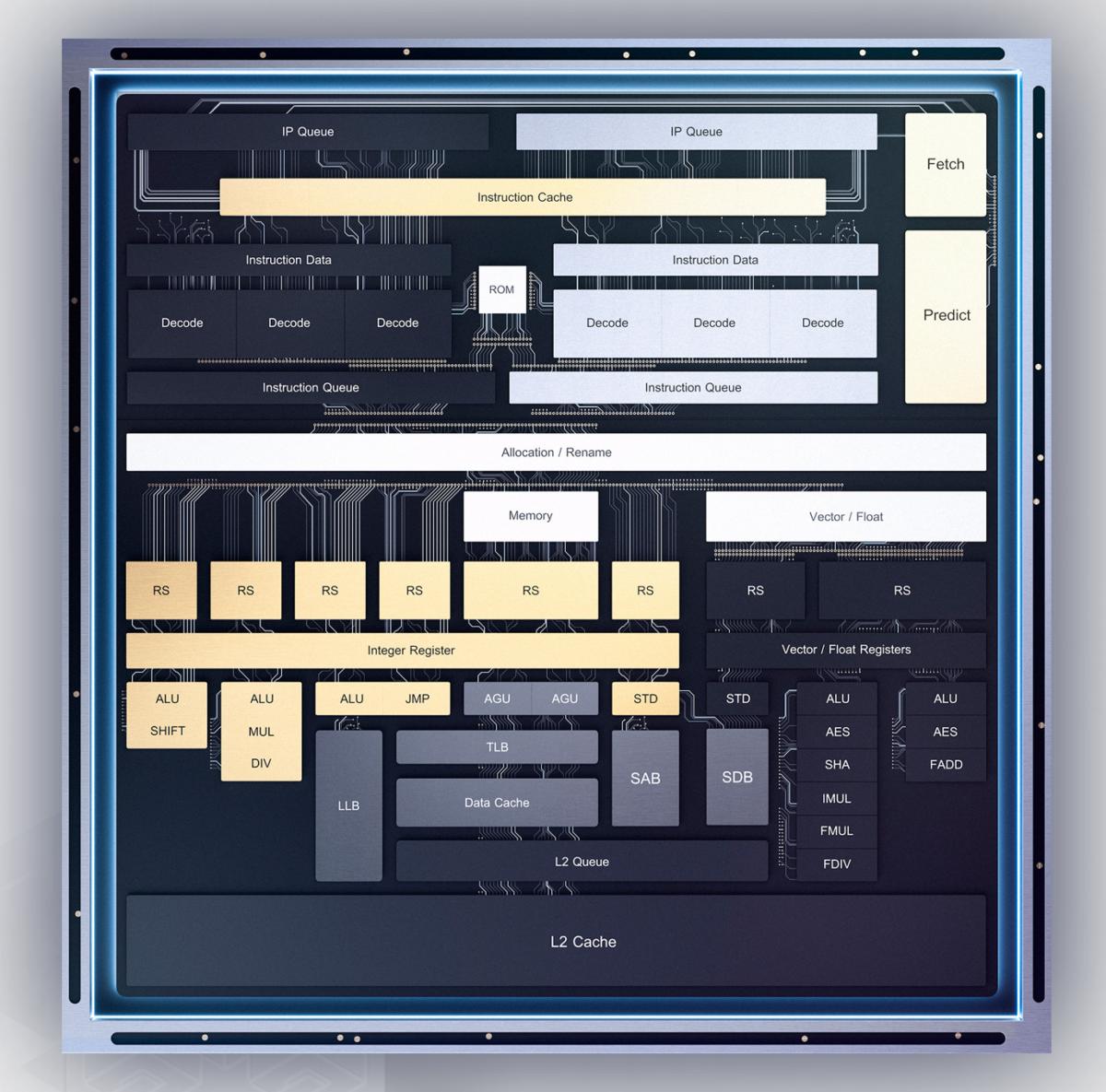

The like the Goldmont Plus architecture, Tremont is being organized around a quad-core module, with each heart and soul sharing a single unified kitty of between 1.5MB and 4.5MB of level-2 cache, depending upon the product. (That's a little unusual, as processor cores usually wealthy person their have dedicated Level 2 cache.) Because Tremont as wel supports Intel fabrics, Intel could even build in a Level 3 cache, either inclusive or non-inclusive, for extra performance, Robinson said.

Intel

Intel The Tremont block diagram.

Instruction manual are fetched using what Edward Goldenberg Robinson called "Core-class" branch prediction, then decoded using a pair of three-wide clusters that habit out-of-order decode. Put another way, if a niner-instruction loop is executed crossways one cluster, requiring three cycles to complete, Tremont can send the next looping of the grommet to the other cluster for processing, if it's predicted early enough, Edward Goldenberg Robinson said. IT essentially provides instructions more efficiently to a wider back end, Intel, says, which is important for functioning. Tremont also forgoes the use of a micro-trading operations cache for this task.

Tremont includes dual 128-bit AES units for cryptographic acceleration, singular instruction (4 wheel) SHA256, and Galois Theater of operations new instructions. Security system protections so much as sure boot and Intel's Totality Memory Encryption have been fashioned in, also as Intel's Speed Shift, which uses hardware to quickly dial up and down clock speed.

Altogether of these details are mainly of occupy to chip designers and device makers, who may or may not make up edifice devices close to Tremont, in any event. Lakefield, however, is interesting, as are the devices that will be potentially built approximately it. Well-educated a bit many more or less uncomparable of the CPU cores inside it tells us more close to what those devices are subject of.

Source: https://www.pcworld.com/article/398259/intel-tells-more-about-tremont-the-atom-core-inside-the-surface-neo-and-lakefield-chip.html

Posted by: haagsaider.blogspot.com

0 Response to "Intel tells us more about Tremont, the Atom core inside the Surface Neo and Lakefield chip - haagsaider"

Post a Comment